你好,我是邵巍。

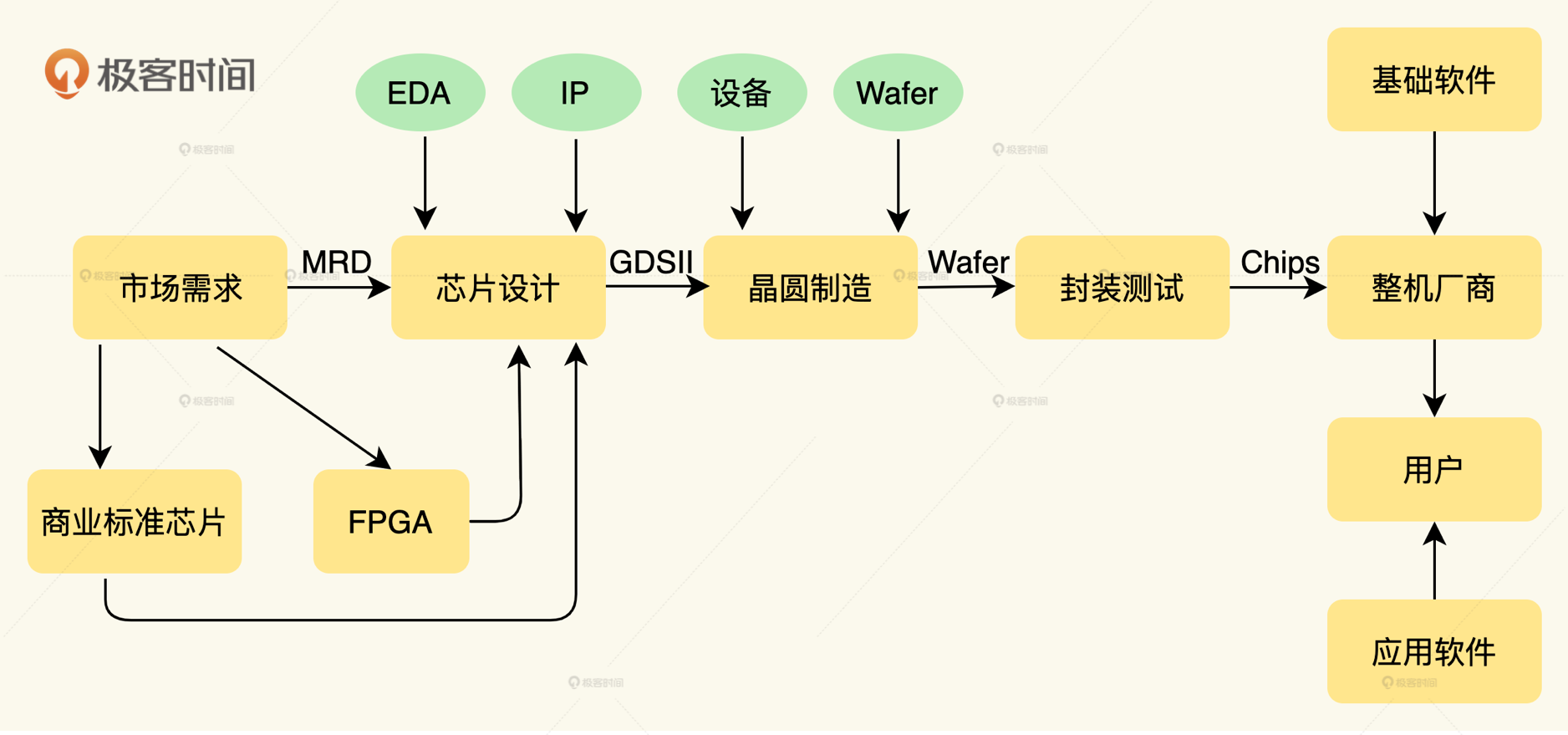

上一讲,我带你从市场需求分析开始,完成了一颗芯片的设计。但是到此时,这颗芯片,还是一个纸上的产品,这一讲,我就带你从晶圆制造到封装测试,历遍芯片的完整制造流程。

芯片是这个世界上最复杂的工程,也是最高精尖的制造工艺。上一讲我跟你说过iPhone的A11处理器,大约在88平方毫米的面积上,集成了43亿个晶体管。43亿个晶体管是什么概念呢?如果一秒钟制造一个晶体管的话,制造43亿晶体管需要136年。

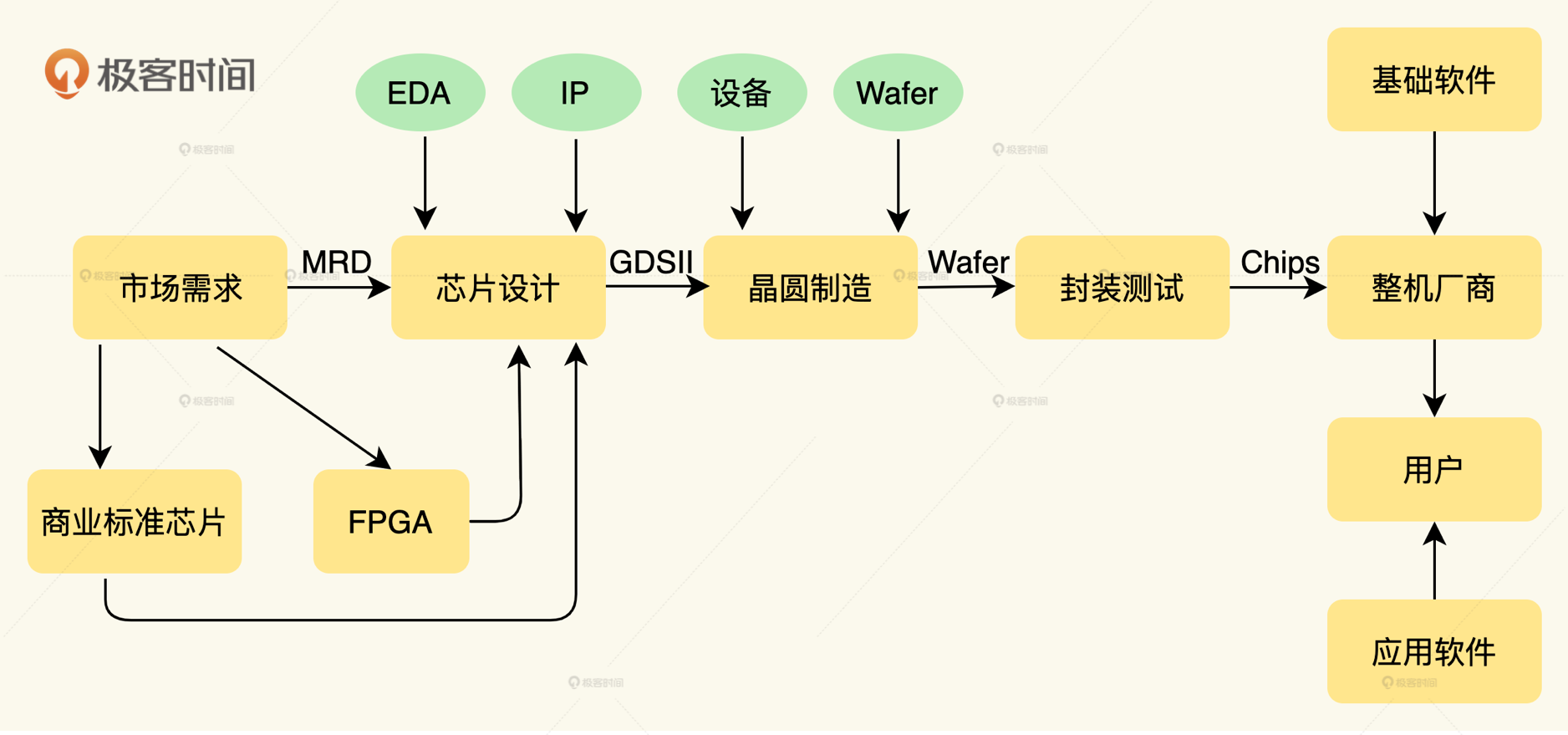

如果仔细看每个晶体管,都是由硅基底(Silicon Substrate)、氧化层(Oxide)、鳍(Fin)、栅(Gate)构成的。鳍的高度,宽度都在十几、几十纳米;栅极长度,高度也在几十纳米的范围之内,是非常精致的纳米级器件。下图已经是简化过的抽象模型,随着半导体工艺的演进,实际的器件,其实比下图要更加复杂。

而芯片的制造,就是要在平方毫米的尺寸上,制造上亿个纳米级晶体管的过程。我们在讲芯片的物理实现的时候说过,每个晶体管,都是被工程师们精心设计,放置在特定的位置上,要完成一定功能的,因此在制造过程中,任何一个晶体管的失效,都会导致最终芯片的一部分,或者整个芯片的失效。

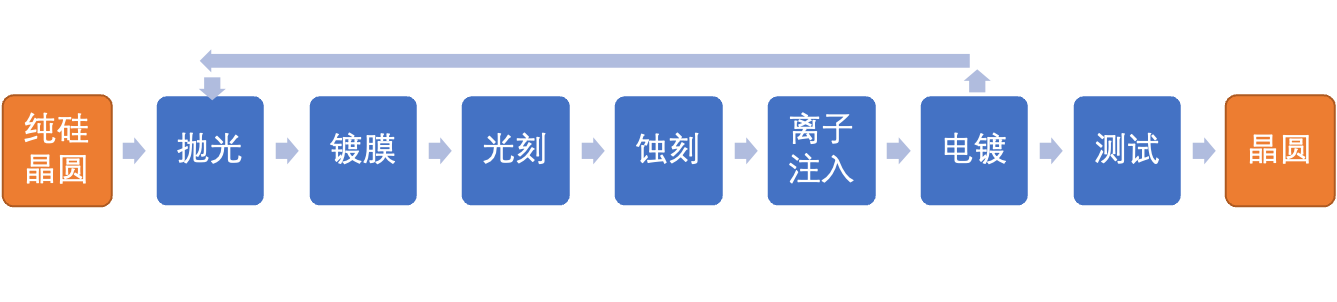

对于整个芯片的制造过程,我给你分了三个步骤让你理解,包括上游的晶圆材料准备,中游的晶圆加工,和下游的封装与测试。开头我给你展示了一张流程图,图中把晶圆制造和封装测试分成两步了,这里我换一种说法,分为上中下游,你也许能更好理解。我们一步一步来拆解。

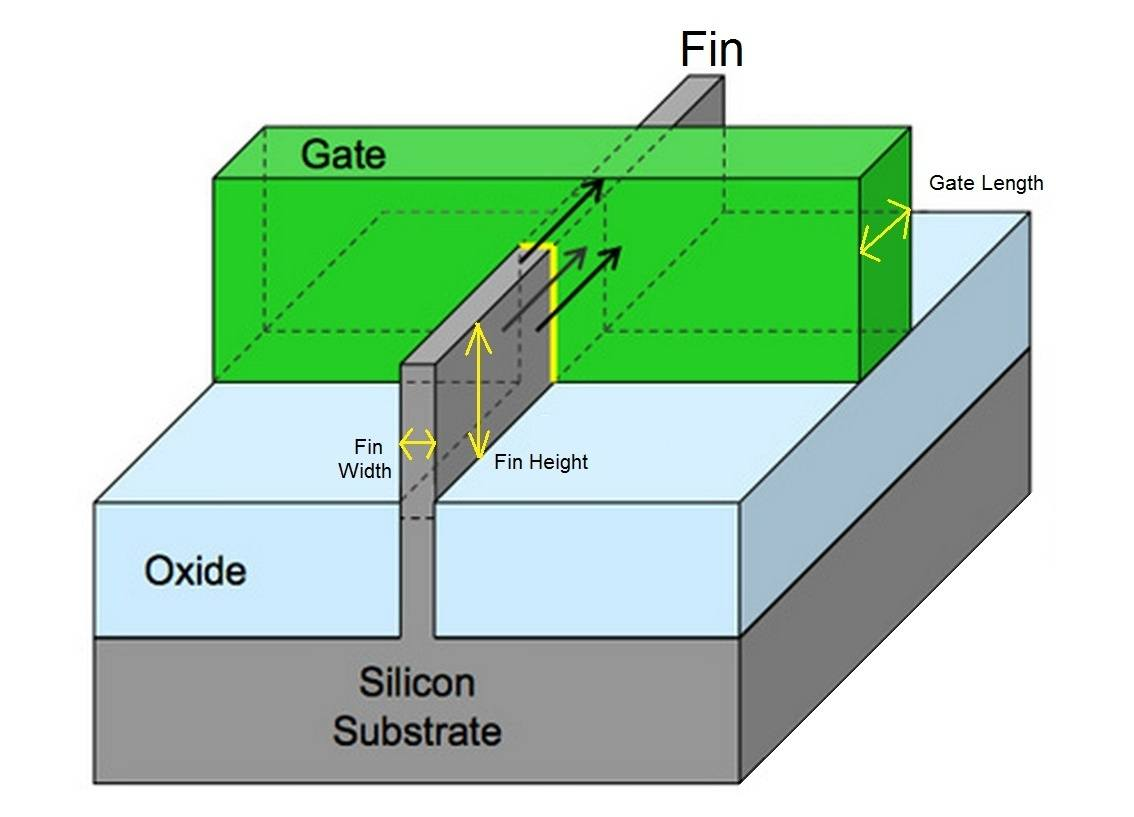

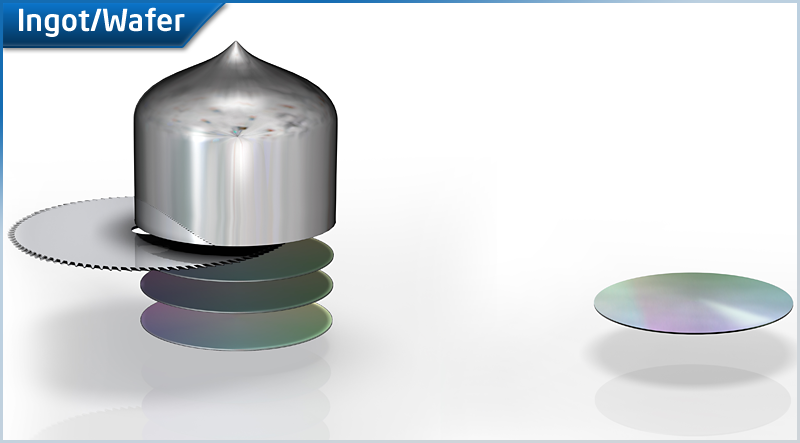

这阶段的重点是提炼单晶硅锭。生产单晶硅锭的公司会将硅元素,从沙子中提取出来,经过高温整形、多次提纯等手段得到高纯度的硅(EGS)。然后再将纯硅熔化,抽出圆柱形的单晶硅锭。

硅锭切割之后,变成一片一片的圆盘,再经过打磨抛光,一片纯硅晶圆,就准备好了。

直径为300毫米的纯硅晶圆,俗称12寸晶圆,大约是400美金。但尺寸并不是衡量硅晶圆的最重要指标,纯度才是。日本的信越公司可以生产13个9纯度的晶圆。

其实,日本的信越、SUMCO(三菱住友株式会社),在晶圆市场上占据了近60%的市场份额,这让晶圆市场排名第三的台湾环球晶圆非常有压力,在2020年开展了并购排在第四的德国世创的计划。

其实半导体产业的上游原材料,不仅仅是晶圆,像在光刻胶、键合引线、模压树脂及引线框架等重要材料方面,日本的企业在全球都占有很高份额。可以这么说,如果没有日本材料企业,全球的半导体制造都要受挫。因此2019年日本限制向韩国出口三种半导体核心原料(含氟聚酰亚胺、高纯度氟化氢、光阻剂)时,曾经一度让三星实际掌门人不得不四处奔走,为保证生产而努力。

有了硅晶圆,下一步就是把设计团队交付的电路图,通过光罩,移植到硅晶圆上。这个加工过程,有上百个步骤,一般需要2到5个月。感谢现代社会的精细分工,即使是半导体从业人员,甚至是在晶圆厂工作的人,只要不涉及工艺的研发,也无需完全掌握这些步骤,只需要各司其职,共同协作就好。

我把加工的过程简化为7个步骤,给你逐步讲解一下。

第一步,纯硅晶圆,在加工之前, 需要打磨抛光。

第二步,抛光完成后,通过高温,或者其他方式,在晶圆表面产生一层薄薄的二氧化硅保护膜,叫做镀膜。

第三步,光刻,光刻是整个过程中最重要的一个环节。这个环节的重要性体现在两个方面,第一,它是设计和制造进行联系的唯一环节;第二它是最昂贵的一个环节。

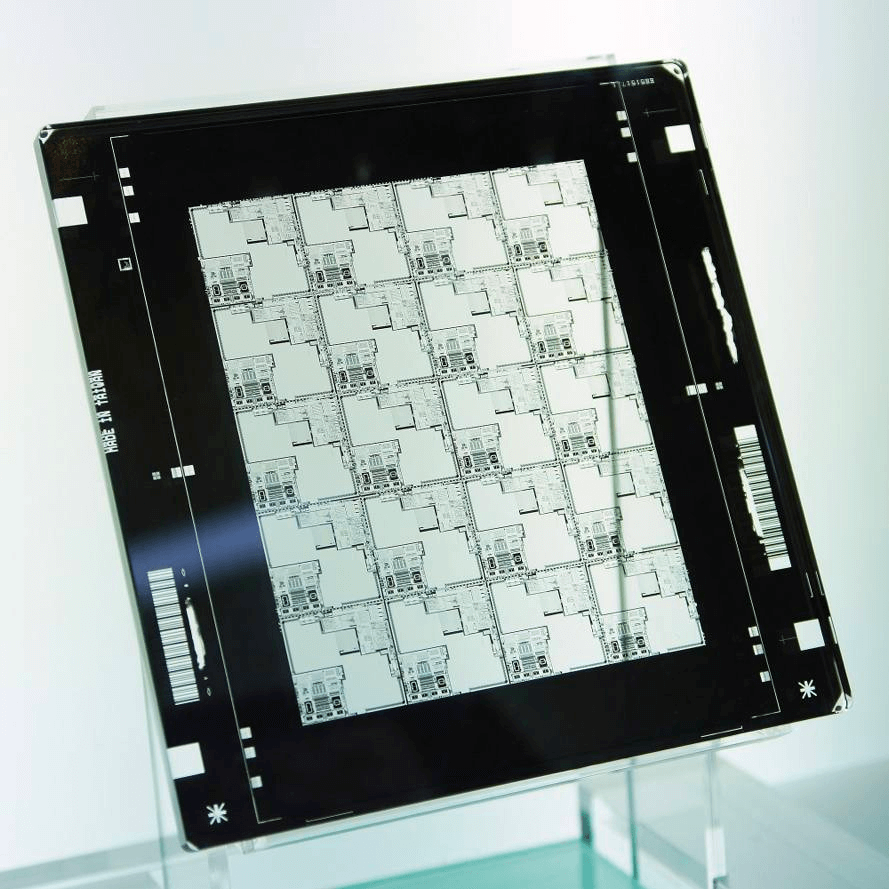

光刻的一个重要输入是光罩。在上一讲中,设计团队交付的GDS II文件,会被用来制成如下的光罩。这个光罩,有点像印钞时候的母版,也是设计和制造之间的纽带。

光罩,有专业的公司可以生产。因为光罩和晶圆制造紧密衔接,所以一般晶圆制造厂,都有自己的专业工厂来生产自身需要的光罩。为了制造一款芯片需要上百道工序,光罩也是不只有一张的,在14nm工艺制程上,大约需要60张光罩,7nm可能需要80张光罩甚至更多。光罩层数的增加,也就代表着成本的增加。工艺提升,带来的光罩层数的增多,算是先进工艺成本越来越高的原因之一。

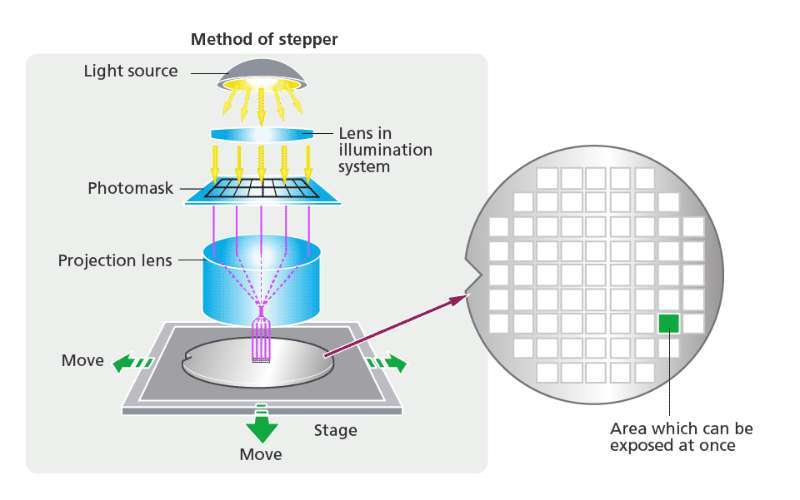

使用特定波长的光,透过光罩,照射在涂有光刻胶的晶圆上,光罩上芯片的设计图像,就复制到晶圆上了,这就是光刻,这一步是由光刻机完成的,光刻机是芯片制造中光刻环节的核心设备。你可以把光刻理解为,就是用光罩这个母版,一次次在晶圆上印电路的过程。

刚刚我说,光刻是最贵的一个环节,一方面是光罩越来越多,越来越贵,另一方面光刻机也很贵。光刻机是半导体制造设备中价格占比最大,也是最核心的设备。2020年荷兰公司ASML的极紫外光源(EUV)光刻机每台的平均售价是1.45亿欧元,而且全世界独家供货,年产量31台,有钱也未必能买得到。

回顾光刻机的发展历史,从1960年代的接触式光刻机、接近式光刻机,到1970年代的投影式光刻机,1980年代的步进式光刻机,到步进式扫描光刻机、浸入式光刻机和现在的深紫外光源(DUV)和极紫外光源(EUV)光刻机,一边是设备性能的不断提高,另一边是价格逐年上升,且供应商逐渐减少。

到了EUV光刻机,ASML就是独家供货了。

EUV作为下一代技术的代表,不需要多重曝光,一次就能曝出想要的精细图形,没有超纯水和晶圆接触,在产品生产周期、光学邻近校正(OPC)的复杂程度、工艺控制、良率等方面的优势明显。是7nm以下工艺必备的。

光罩加光刻机,让光刻这个步骤 “贵”了起来。

好,光刻之后,就到了第四步蚀刻,蚀刻就是去除多余物质。

第五步,离子注入,在真空的环境下进行离子注射,在光刻的晶圆电路里注入导电材料,这样可以改变对应区域的导电特性。

第六步,电镀,电镀这个步骤主要是用来制作铜导线的。

一颗芯片通常有多层,每一层的线路不同,功能不同,使用的膜的材质不同。所以每一层的光罩也不同。因此,以上的1-6步需要根据实际的集成电路的设计层数重复进行几次到数十次。这里可以有一个小知识点,如果芯片有一些小Bug,可以只对其中几层的光罩进行修正,而不用重做全部的光罩。

第七步,测试,测试永远是重要环节。对于晶圆的测试可以分成两类,一类是制造工艺相关的晶圆验收测试,一类是电路功能测试。当然,当晶圆切割完毕,在封装之前,还会再进行测试。不过对于整个晶圆进行测试,效率要高过切割之后。

这里我们可以复习一下上一讲逻辑设计中提到的DFT环节。在进行电路的前端设计时,就预先设计并插入用来测试的电路,这就是DFT。后期,无论是晶圆的电路功能测试,还是封测阶段中最后的测试,都是依赖DFT设计的。

芯片制造的中游环节,到这里就介绍完了。我一定要提一下价值问题,这么昂贵的工厂制造环节,究竟可以增值多少呢?据国际商业策略IBS公司(International Business Strategies)的推算,台积电一片5nm晶圆的加工费高达12500美金。根据台积电的财报推算,台积电平均每片晶圆可以产生近4000美金(300mm晶圆)的利润。无论是哪个数字,对比400美金的纯硅晶圆原料来说,这都是一个至少增值10倍的高价值的加工过程。

当晶圆制造进行测试之后,就会被送往下游的IC封装测试厂实施切割、封装和进一步的测试。

整个晶圆在切割成单片之后,会针对每一个单片(芯片)进行电气测试。在封装前,还会使用显微镜对芯片进行复检。提前检测出有瑕疵的芯片,可以减少后续流程上的成本开销。

封装的主要目的是将半导体材料集中在一个保护壳内,防止物理损坏和化学腐蚀。相对于测试,封装对芯片的最终形态,影响更大。

半导体封装技术有三次大的技术进步:第一次是在 20 世纪 80 年代从引脚(Pin)插入式封装到表面贴片封装,表面贴片封装极大地提高了印刷电路板上的组装密度;第二次是在 20 世纪 90 年代球型矩阵封装的出现,满足了市场对高引脚的需求,改善了半导体器件的性能。

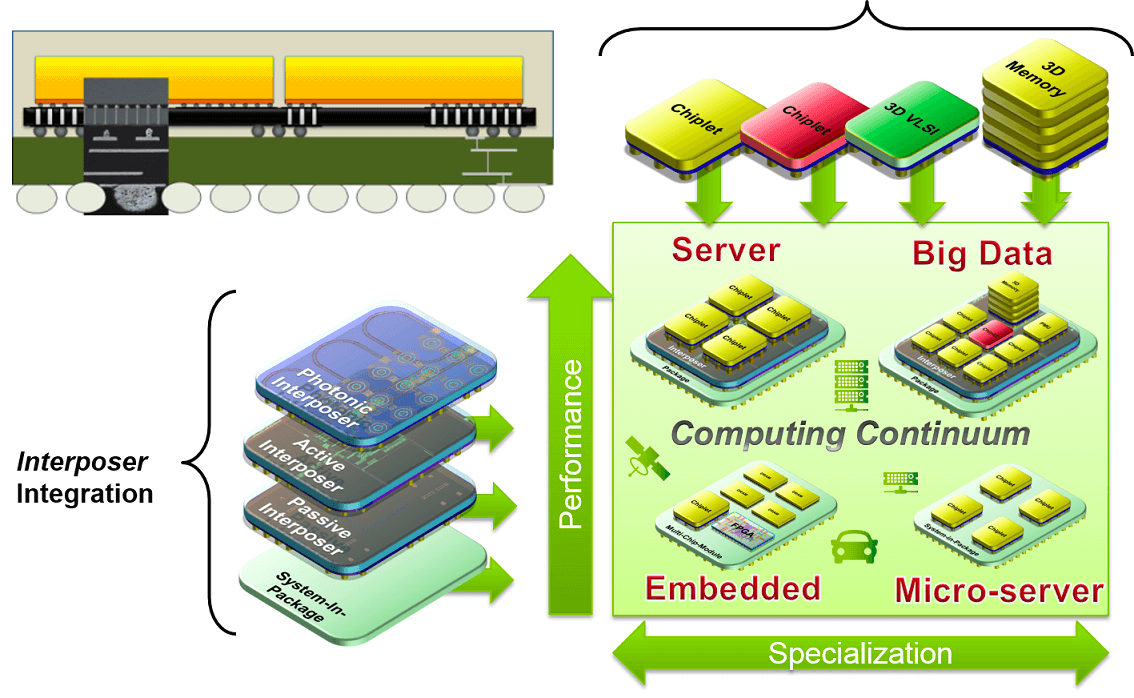

第三次是2D、2.5D、3D封装等,混合了芯片堆叠、异构封装的先进封装。先进封装的最主要推动力来自手机,因为手机有着对封装面积最小的极致追求,其次推动力来自于数据中心对高性能芯片的追求。

关于2D、2.5D、3D封装,我有一个朋友有个非常形象的比喻,“摊大饼摊不下去了,搞个千层饼试试”。总之,所谓的先进封装,就是把单独设计和制造的组件或者小芯片(chiplet),封装在一起,如下图。

封装之后,还会对每个芯片进行最后的测试。这个环节是由ATE专业自动测试设备完成的。因为一般的公司,都是租用ATE机台,所以每个芯片的测试计划,测试时间等,都是成本的一部分。一般的经验是,一颗芯片的1/3的成本,是花在封测阶段的。

基于测试的结果,将具有相同能力的芯片归属一类,可以根据芯片的最高工作频率,稳定性等规格制定等级,以便定价。该芯片就会被打标示,分类芯片的规格、型号及出厂日期等丝印,等待打包出厂了。有部分缺陷的芯片,在很多时候是可以作为低规格的正式产品出厂的。要做到这点,必须在架构设计阶段,就要规划好。一个优秀的架构师,考虑的不仅仅是功能和性能的竞争性,整个流程中的每一个与芯片成本相关的问题,都必须提前考虑周到。

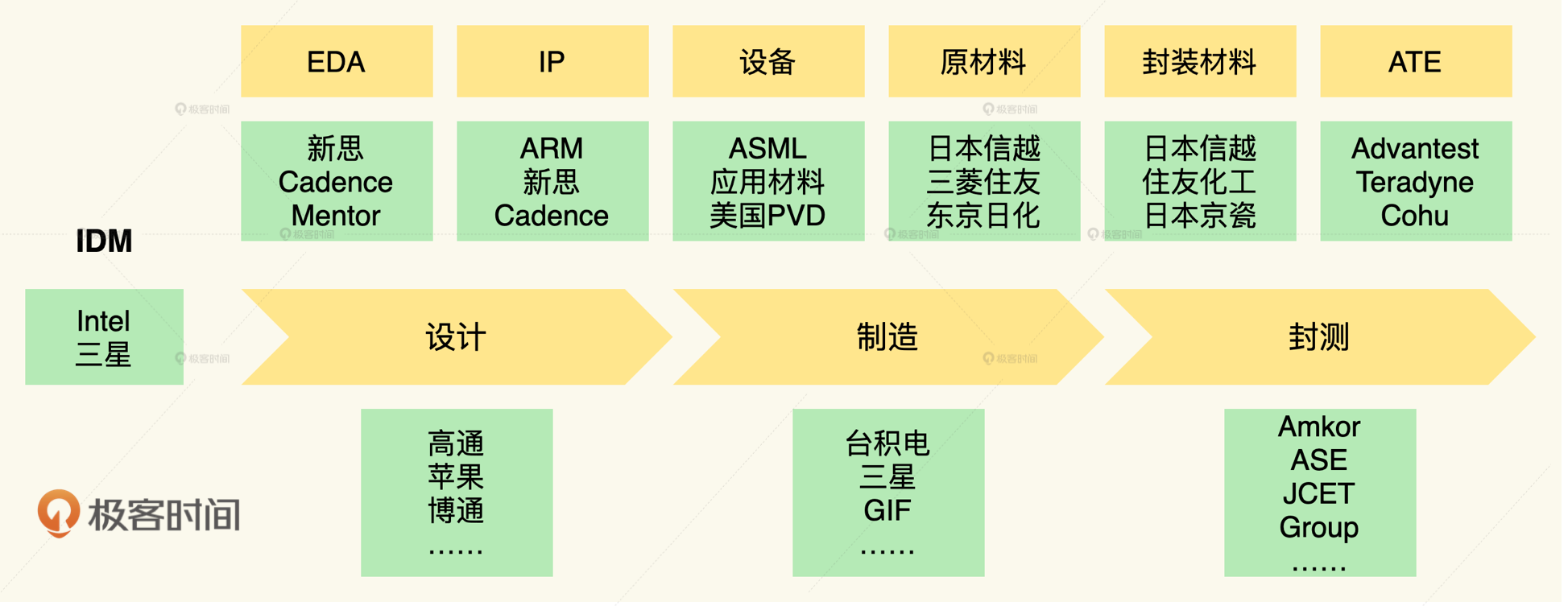

到这里,芯片制造的过程我就讲完了,目前除了极少数半导体设计公司还有工厂之外,芯片的制造是都由专业的晶圆厂代为制造,是晶圆厂的王国领地。上一讲我们提到的芯片设计,和这一讲分析的芯片制造与封测,并不需要一个公司完成,我给你总结了一个产业链的分工合作示意图:

在半导体行业开始的三十多年,所有的半导体公司,都是从设计到制造全部自己完成。在下一讲介绍Intel的时候,我会提到当IBM向Intel订购芯片,Intel会设计、制造、测试、封装,然后直接交付芯片。这种模式业界称为集成设备制造商,也就是IDM模式。

这种模式,在1987年台积电创立之后,慢慢地改变了。台积电这样的代工厂,专注于芯片制造这个环节,服务整个半导体产业。越来越多的创业公司,选择放弃需要高额资金的建厂环节,专注在价值更高的设计芯片环节。设计和制造开始了分离。

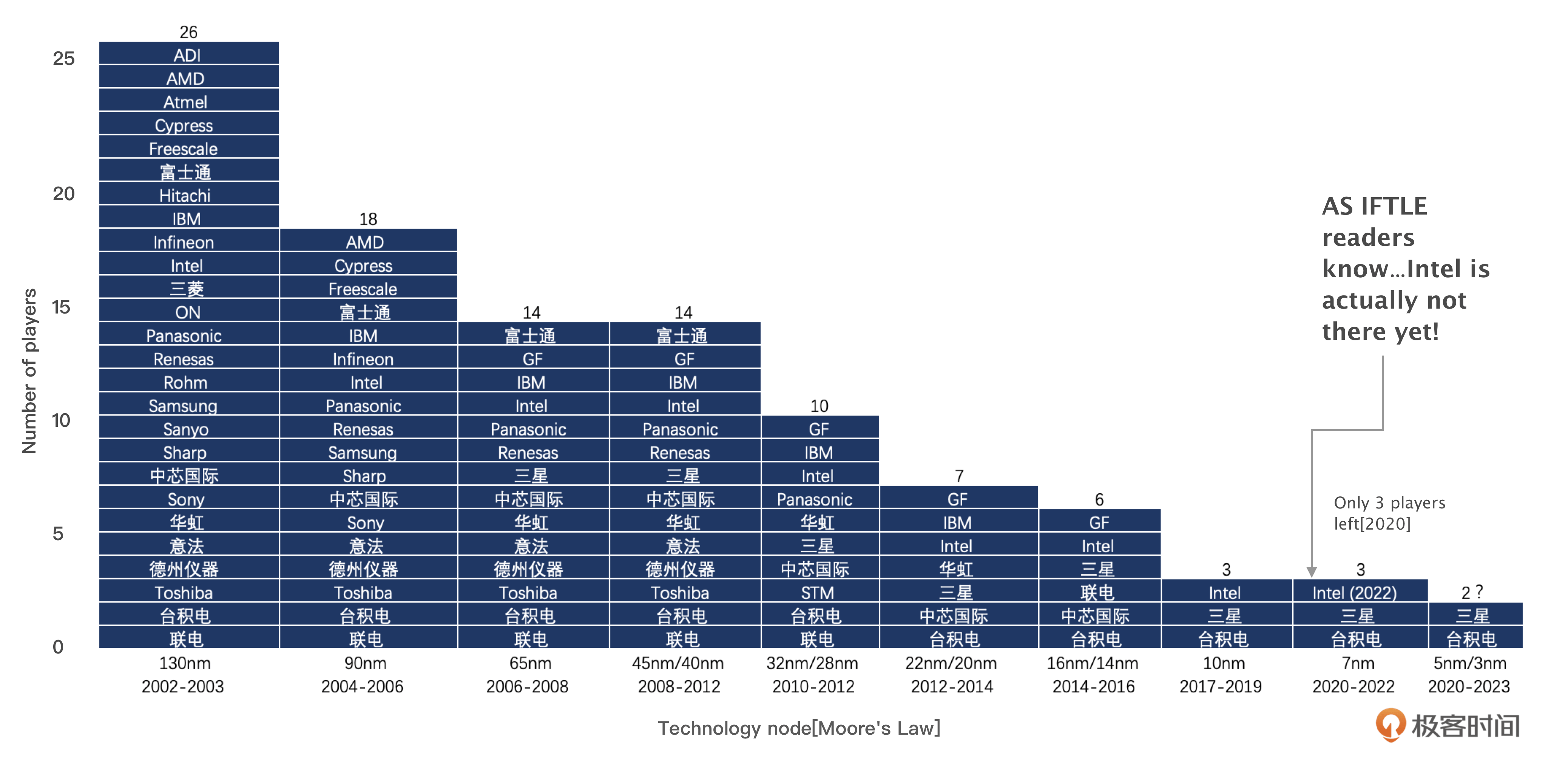

在摩尔定律的推进下,半导体行业高速运转,半导体工艺从45nm,到28nm,到16nm不断演进,随着晶体管体积不断变小,建造工厂的成本剧增。能够维持一定的生产规模,进行良性的商业循环的IDM模式公司在减少,甚至专业的晶圆厂都在逐步减少之中。

下图是一张工厂对应工艺制程的总表。到了10nm工艺制程的时候,全世界晶圆厂也就只有三家了。

那些原来的IDM模式的公司都怎样了呢,有的完全剥离工厂,成为无厂的纯设计公司,例如AMD、IBM。有的放弃跟随新工艺,成为轻工厂模式,例如博通,德州仪器。

制造和设计分离之前,技术和资本门槛都略低的封测环节,就已经被分离,且向人力资源成本便宜的亚洲转移了。半导体行业是全球化分工最早最彻底的行业之一。这也是中美之争中,芯片行业会成为一个焦点的原因。

这一讲我分享了蛮多内容,下面简单总结一下。

最后,关于芯片制造,Intel有一个形象的动画视频,很不错,推荐你看一下。

芯片的制造环节究竟有多重要?美国公司放弃IDM模式,将生产制造环节转到亚洲的这个做法,是正确的么?欢迎你给我留言。

评论